Descrivere il funzionamento dell’inverter CMOS e discutere le differenze tra l’inverter reale e ideale.

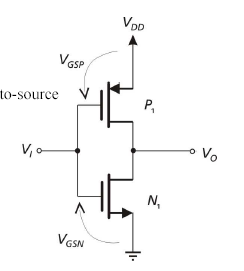

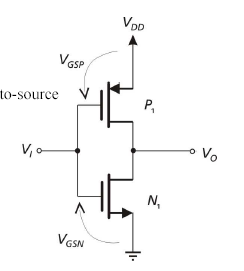

Figura 1.1: Schema elettronico dell’inverter CMOS

L’inverter è costituito da una coppia di MOSFET complementari. Più in dettaglio si compone di un PMOS messo in serie ad un NMOS.

Entrambi i dispositivi sono pilotati e quindi il carico rappresentato dal PMOS è variabile non solo in dipendenza della tensione ai suoi capi ma anche e principalmente a causa della tensione al suo ingresso. Mentre la tensione di gate VGsn dell’NMOS è data dall’ingresso Vi, quella del PMOS VGsp è data da Vi–Vdd. Un aumento dell’ingresso Vi porta contemporaneamente in maggior conduzione N1 e in minor conduzione P1, con effetto cumulativo per la variazione della tensione di uscita

|

|

transitore Tp interdetto |

transitore Tn in conduzione |

|

|

transitore Tp in conduzione |

transitore Tn interdetto |

Vi = Vdd

|

|

NMOS conduce se VGsn > Vtn > 0 PMOS conduce se VGsp < Vtn < 0

Quindi si ha

Vi = Vdd V0 = 0 |

Vi = 0

|

|

VGSN = 0 NMOS spento

VGSP = -VDD<VTp<0 PMOS acceso

Vi = 0 Vdd = 1

|

|

Vi = Vdd |

|

Vi = 0 |

|

|

VGsn = Vdd |

N1 conduce |

VGsn = 0 |

N1 interdetto |

|

VGsp = 0 |

P1 interdetto |

|VGsp| = Vdd |

P1 conduce |

|

Idp = Idv =0 |

Corrente nulla |

Idp = Idv = 0 |

Corrente nulla |

|

Vol =0 |

Uscita bassa |

Voh = Vdd |

Uscita alta |

Tabella

1: Punti di funzionamento per i valori limiti

di ingresso

Relazioni corrente tensione dei transistori

Per Tn

![]()

![]()

![]()

![]()

Per Tp

![]()

![]()

![]()

![]()

I coefficienti K sono legati alle caratteristiche fisiche e geometriche secondo le espressioni

![]()

![]()

L’invertitore CMOS viene

progettato in modo tale da avere le stesse tensioni di soglia per

entrambi i transistori ovvero Vtn = |Vtp| = Vt ed anche Kn = Kp = K.

Poichè nel silicio

μn = 2.5 μp si conclude

che per ottenere l’uguaglianza dei fattori di forma è

necessario dimensionare il canale del PMOS di larghezza 2.5 volte

rispetto a quella dell’NMOS.

In questo modo si ottengono le

stesse correnti per entrambi i transistor ed una caratteristica

simmetrica, al prezzo di avere un NMOS di area 2.5 volte quella del

PMOS con un maggiore spreco di silicio. Con entrambi i transistori

saturi la caratteristica assume una pendenza verticale grazie

all’elevata resistenza d’uscita. Se i transistori fossero

della stessa dimensione (sia L che W) si perderebbe la simmetria con

conseguente peggioramento dei margini di rumore

Figura

2: transistori della stessa dimensione:

Perdita della

simmetria con conseguente peggioramento dei margini di rumore

Figura 3: Costruzione grafica della caratteristica di trasferimento per un invertitore CMOS

Figura

4: Segnale simmetrico, scomposizione del

segnale in base alle zone di funzionamento

Se i MOS sono simmetrici, la caratteristica di trasferimento dell’invertitore viene ottimizzata

|

Tratto |

Descrizione |

PMOS |

NMOS |

|

A-B |

tensioni Vi inferiori alla soglia Vt |

interdetto |

conduce |

|

B-C |

Transistore N comunica e conduce. Uscita corrisponde all’intersezione con P nella regione di triodo e N in quella di Pinch-off |

Regione di triodo |

Regione

di |

|

C-D |

I 2 MOS lavorano nella regione di pinch-off |

Regione

di |

Regione

di |

|

D-E |

|

Regione di pinch - off |

Regione di triodo |

|

E-F |

|

interdetto |

conduce |

|

|

|

|

|

|

Figura

5. Costruzione del segnale

L’assunzione di Kn = Kp permette di ottenere una caratteristica di trasferimento simmetrica e i margini di rumore NMh= NMl (situazione ottimale per un invertitore). Il comportamento dinamico dell’invertitore CMOS dipende dalla capacità di carico in uscita. Questa capacità tiene conto delle diverse capacità connesse al terminale di uscita. L’invertitore CMOS presenta una dinamica migliore di quella di un invertitore NMOS, ciò principalmente a causa del fatto che i tempi di propagazione tpHL e tpLH sono uguali in base all’uguaglianza delle due correnti di carica e scarica della capacità.

Il ritardo di propagazione dipende solo dal quadrato della lunghezza di canale (Ln^2), mentre la scelta di Wn non ha influenza. Ne discende quindi che la scelta migliore per Ln e Lp è sempre quella della minima lunghezza di canale, compatibilmente con le regole di progetto utilizzate per ridurre l’occupazione di area.

Figura

6: Ritardo di propagazione di un inverter CMOS

Riguardo alla potenza dissipata sia per l’ingresso alto (Vdd) che basso (0), la corrente nell’invertitore CMOS è nulla per cui non vi è dissipazione staica di potenza in nessuno dei due stati possibili. La potenza dissipata dalle porte corrisponde quindi solo a quella dinamica, cioè quella relativa alle transizioni da uno stato all’altro. Questa potenza dissipata a sua volta viene a dipendere da due cause

Corrente che circola nei due MOS nelle fasi di transizione in cui tutti e due i MOS sono in conduzione

Corrente che carica la capacità d’uscita